#### DEPARTMENT OF COMPUTER SYSTEM ENGINEERING Digital Integrated Circuits - ENCS333

Dr. Khader Mohammad Lecture #13

Timing

## **Digital Integrated Circuits**

|    | 0 0                                                         |

|----|-------------------------------------------------------------|

|    | Course topics and Schedule                                  |

|    | Subject                                                     |

| 1  | Introduction to Digital Integrated Circuits Design          |

| 2  | Semiconductor material: pn-junction, NMOS, PMOS             |

| 3  | IC Manufacturing and Design Metrics CMOS                    |

| 4  | Transistor Devices and Logic Design                         |

|    | The CMOS inverter                                           |

| 5  | Combinational logic structures                              |

| 6  | Layout of an Inverter and basic gates                       |

|    | Static CMOS Logic                                           |

| 8  | Dynamic Logic                                               |

| 9  | Sequential logic gates; Latches and Flip-Flops              |

| 10 | Summary : Device modeling parameterization from I-V curves. |

|    | Interconnect: R, L and C - Wire modeling                    |

| 12 | Parasitic Capacitance Estimation                            |

|    | Timing                                                      |

| 14 | Power dissipation;                                          |

| 15 | Clock Distribution                                          |

| 16 | Arithmetic building blocks                                  |

| 17 | Memories and array structures                               |

| 18 | Reliability and IC qualification process                    |

| 19 | CAD tools and algorithms                                    |

| 20 | Final & Project discussion                                  |

|    | , i i i i i i i i i i i i i i i i i i i                     |

|    |                                                             |

## Agenda

- Intro (What is timing all about)

- Static timing versus dynamic timing

- Timing primer

- Flop based timing

- How clock uncertainty impacts timing analysis

- Latch based timing (transparency, time borrowing, time borrowing FFs etc)

- What is a design window?

- Gated clock & domino timing

- Phase paths, MCPs & cycle adjusted margins

- Understanding EVRs & BVRs

- Full chip rollups and slack allocation

- Advanced Topics (loop paths, zero-cycle paths)

# What do we mean by "Timing" ?

- Timing Analysis is a method of analyzing and solving timing problems to ensure that the design meets the target frequency.

- A circuit meets target frequency when all of the signals:

- Arrive just before they are needed.

- Remain until no longer needed.

- Be guaranteed stable in between.

- Critical paths are paths in the circuit along which the signal doesn't reach its destination on time; this causes the functionality of that part of the circuit to be impaired.

## Static Timing

Static timing analysis computes the worst case delays for paths in a given circuit.

It is a non-simulation approach to timing analysis used to analyze the propagation of delays.

Pathmill and Tango-XT are examples of static timing tools.

# Static Timing

- Searches path by path. Performs static timing analysis (STA) of a circuit by analyzing the circuit in a non-simulated way (no input vectors.)

- Traverses all possible paths between each source-sink pair.

- Calculates the path delay and the arrival time at each signal along the path and internal sampling requirements.

- Sorts the paths by the amount of violation at their sink node and prints them in a report.

- Report can be used to:

- Determine how to fine tune the timing of the design to meet the target frequency

- Analyze timing violations and performance bottlenecks in circuits.

# Static vs. Dynamic Timing

- Static timing Analysis:

- Non simulation approach used to analyze propagation of delays.

- Computes worst case path delays by accumulating pre-characterized device delays along a given path.

- Path determination is based on the possibility of an event on a device input causing an event on a device output.

- Dynamic Timing Analysis:

- Circuit simulation approach that obtains a very accurate timing analysis of a path.

- Uses input waveforms and path sensitization, generates output waveforms.

#### Comparison of Static vs. Dynamic Timing

| <ul> <li>Static (path analysis)</li> <li>No input vectors; full coverage</li> </ul> | <ul> <li>Dynamic (simulation)</li> <li>Uses input vectors; coverage</li> </ul>           |  |  |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|

| <ul> <li>Points to exact origin of timing</li></ul>                                 | <ul> <li>depends on vector selection</li> <li>Requires a debug process to find</li></ul> |  |  |

| problems (critical paths)                                                           | the origin of timing problems                                                            |  |  |

| <ul> <li>Ensures full coverage (Much</li></ul>                                      | <ul> <li>Requires a lot of CPU time for</li></ul>                                        |  |  |

| faster than simulation)                                                             | good coverage                                                                            |  |  |

| Relies on approximated models                                                       | <ul> <li>Highest degree of accuracy</li></ul>                                            |  |  |

| which are less accurate than                                                        | possible through software                                                                |  |  |

| simulation                                                                          | simulation                                                                               |  |  |

| Inherent problem: false paths                                                       | <ul> <li>Inherent problem: test vector<br/>generation</li> </ul>                         |  |  |

| <ul> <li>Simulates only one input switchin</li></ul>                                | <ul> <li>g • Simulates multiple inputs</li></ul>                                         |  |  |

| at a time                                                                           | switching simultaneously                                                                 |  |  |

| Gives worst case delays only                                                        | Gives precise delay information                                                          |  |  |

# When do we use Static or Dynamic Timing?

Static Timing is used more often due to the size of the designs.

Dynamic timing is typically used where analog behavior is expected and not modeled correctly by static timing.

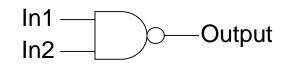

## Static vs. Dynamic Timing: Example 1

- Given a simple two-input NAND gate, static analysis will yield four paths analyzed:

- In1 rising -> output falling

- In1 falling -> output rising

- In2 rising -> output falling

- In2 falling -> output rising

- Given the same NAND gate, dynamic analysis can yield six main transitions. The above four, as well as

- In1 rising & In2 rising -> output falling

- In1 falling & In2 falling -> output rising

- Theoretically, Dynamic Timing has an infinite number of different paths, as the user determines the exact timing of the rise/fall of the inputs in relation to each other.

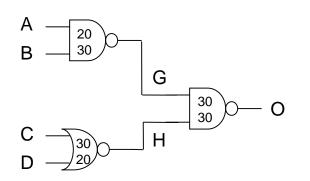

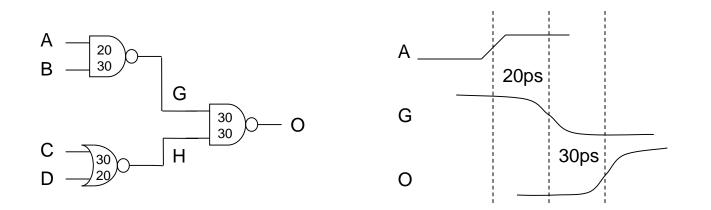

#### Static vs Dynamic Timing: Example2

Path #1 A -> O A Rising -> G Falling -> O Rising 20ps + 30ps = 50ps

Path #2 A -> O A Falling -> G Rising -> O Falling 30ps + 30ps = 60ps

- Static timing analysis is based upon the <u>possibility</u> of a path existing.

- All paths are traversed and delays are calculated.

- These delays are used to check signal arrival times in order to determine setup and hold margin.

#### Static vs Dynamic Timing: Example2 (cont.)

- Using Dynamic Timing on the same example, inputs B, C, and D need to be sensitized to exercise the path: A rising -> G falling -> O rising

- B must be set high

- C and D must be set low

# **Timing Primer**

- Terms we need to learn very very well:

- Reference Clock

- Lead edge signals

- Trail edge signals

- Valid Windows

- Required Windows

- Margin

- Margin Violations

## What is a Reference Clock?

- An ideal clock that does not have jitter or skew

- Generally does not exist anywhere in the design

- All timing is analyzed and specified against a reference clock

- There may be more than one per design

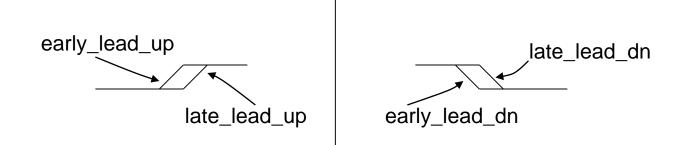

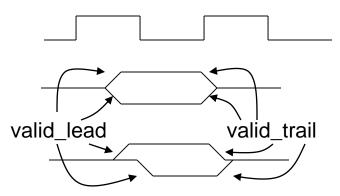

## What are Lead Edge Signals ?

- The lead edge is the time that the signal become stable/active.

- If a signal rises and becomes active, this is **lead\_up**.

- If the signal falls and becomes active, it is a lead\_dn edge.

- A signal may have multiple lead up edges at different times. For this case we can describe them using the terms: early\_lead and late\_lead

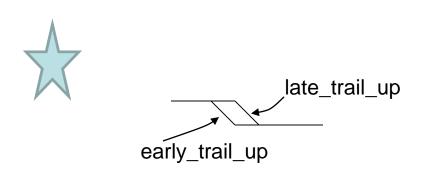

## What are Trail Edge Signals ?

- The trail edge is the time that the signal become inactive (or goes away).

- The **trail\_up** edge (<u>falling edge</u>) refers to the trail edge of the "up" (logical 1) window.

- The **trail\_dn** edge (<u>rising edge</u>) refers to the trail of the "dn" (logical 0) window.

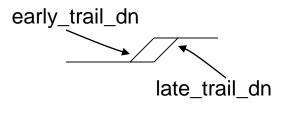

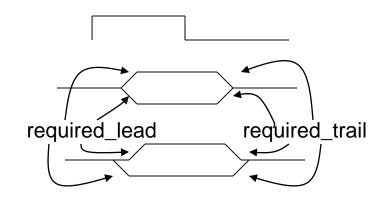

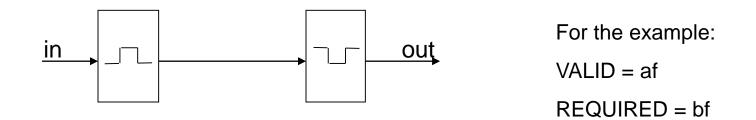

## What are Valid Windows?

- Valid windows are referenced to a clock event and indicate the time when a signal is stable.

- The valid\_lead\_up edge and the valid\_lead\_dn edge need not have the same timing. These edges may come from entirely different paths of logic.

- valid\_lead will correspond to late\_lead

- valid\_trail will correspond to early\_trail

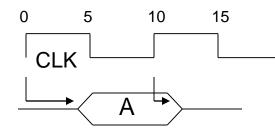

# Valid Window Examples

- Valid times are conventionally specified as

- AR or AF (after rise or after fall)

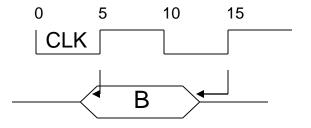

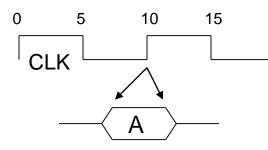

A: valid\_lead = 4 ar CLK valid\_trail = 2 ar CLK B: valid\_lead = -1 ar CLK valid\_trail = -3 ar CLK

## What are Required Windows?

- Required windows indicate the time when a signal must be valid or active to meet timing. This signal must be valid for the whole time of the defined window.

- Required windows come from circuit timing requirements for setup times and hold times.

- required\_lead will correspond to early\_lead

- required\_trail will correspond to late\_trail

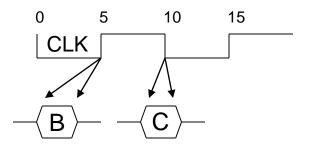

## **Required Window Examples**

Required times are conventionally specified as BR or BF (before rise or before fall)

A: required\_lead = 4 br CLK required\_trail = -3 br CLK

- B: required\_lead = 5 br CLK required\_trail = 2 br CLK

- C: required\_lead = 2 bf CLK required\_trail = -1 bf CLK

#### A Note about Coloring Conventions

- The color (af/ar) of the VALID lead is always referenced to the "opening" edge of the closest sequential element to the output along a path.

- The color (bf/br) of the REQUIRED lead edge is always referenced to the "closing" edge of the closest sequential element to the input along a path.

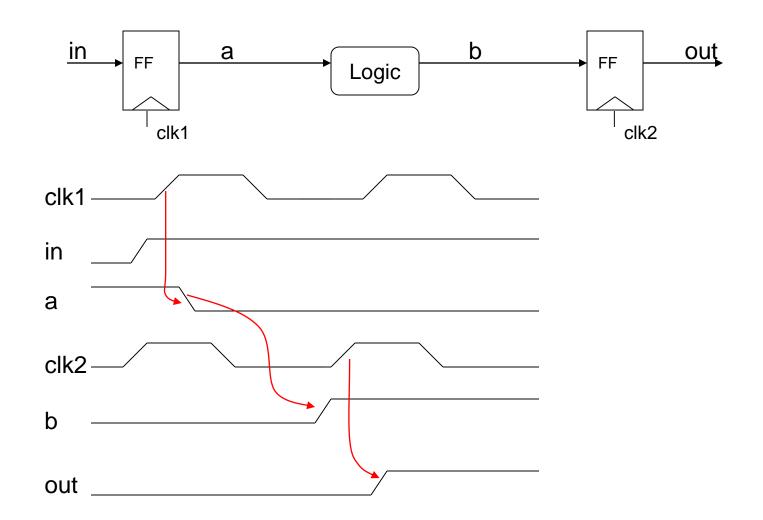

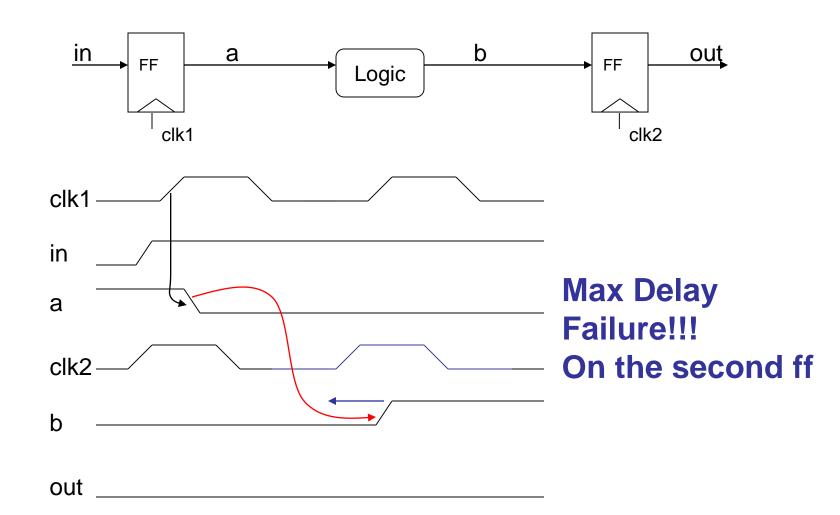

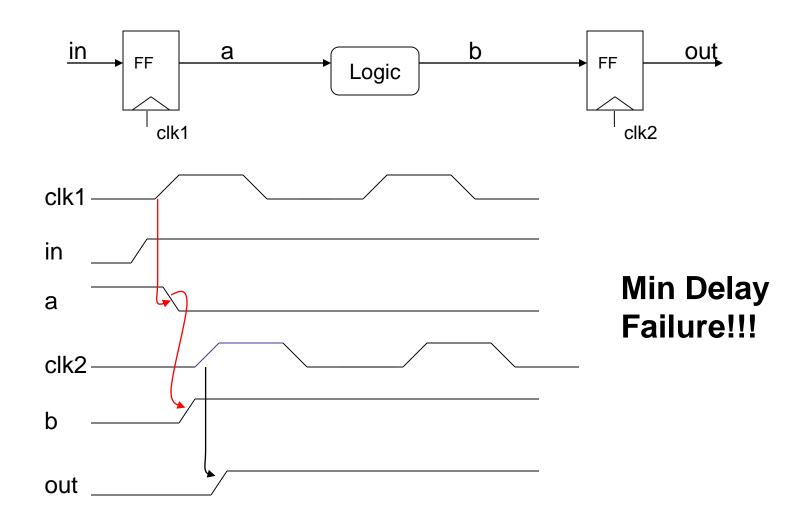

#### Max/Min Delay Margins Example 3

#### Max/Min Delay Margins Example 3 (cont.)

#### Max/Min Delay Margins Example 3 (cont.)

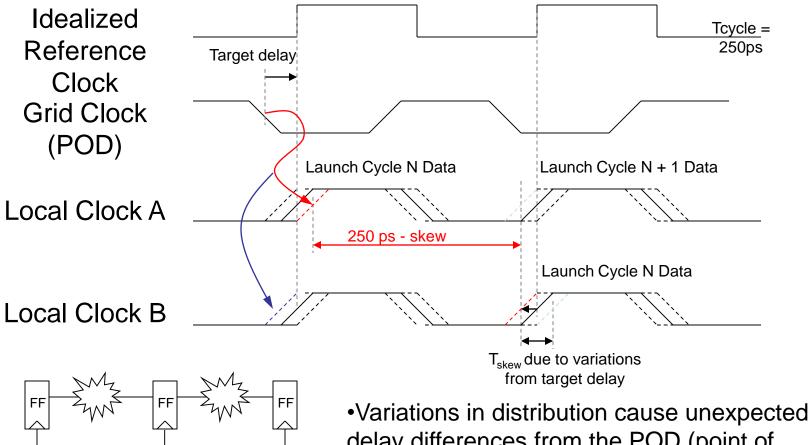

## Sources of Clock Uncertainty

- Skew Unintentional mismatch in the arrival of two local clock edges produced by the same global clock edge. Main causes are:

- RC mismatch in the clock network

- Cross-coupling in the clock network

- (P)rocess, (V)oltage, (T)emperature mismatch in the clock distribution network

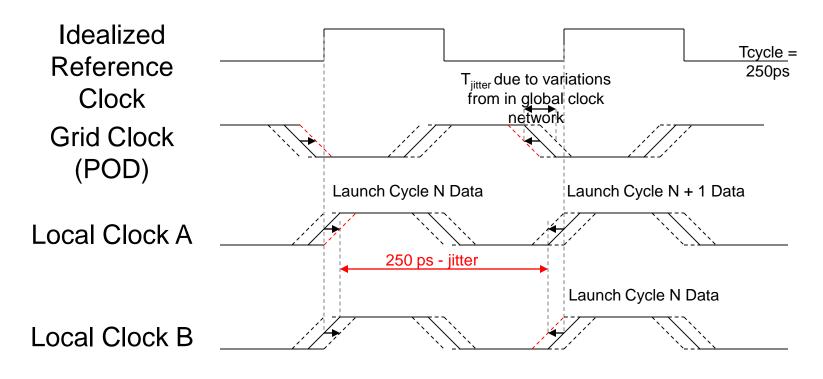

- Jitter\* Variation in the cycle time of the global clock. Main causes are:

- PLL Jitter

- Coupling in the global clock distribution network

#### **Clock Skew Illustrated**

Local

Clock A

Local

Clock B

Local

Clock A

delay differences from the POD (point of divergence) to the local clock @ the sequential •Skew impacts both setup and hold checks

## **Clock Jitter Illustrated**

Variations in PLL & global distribution network cause jitter

Jitter only impacts setup checks

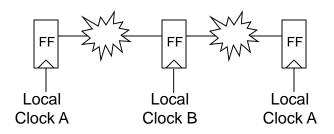

#### How Skew & Jitter Fit in the Setup Margin Calculation

- Without Skew/Jitter

- Margin<sub>setup</sub> = Required<sub>abs</sub> Valid<sub>abs</sub>

- With Skew/Jitter

- Margin<sub>setup</sub> = Required<sub>abs</sub> Valid<sub>abs</sub> MaxSkew

Each cycle pays setup, skew & jitter

## Setup Margin Examples

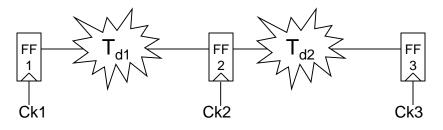

$\begin{aligned} \text{Margin}_{\text{setup FF1->FF2}} &= \text{T}_{\text{cycle}} - \text{Clk->Q}_{???} - \text{T}_{d??} - \text{Setup}_{???} - (\text{ MaxSkew}_{???} + \text{Jitter}) \\ &= 250 - (23 + 185 + 37 + 15 + 16) \\ &= 250 - 276 = -26\text{ps} \end{aligned}$

$\begin{aligned} \text{Margin}_{\text{setup FF2->FF3}} &= \text{T}_{\text{cycle}} - \text{Clk->Q}_{???} - \text{T}_{d???} - \text{Setup}_{???} - (\text{ MaxSkew}_{???} + \text{Jitter}) \\ &= 250 - (25 + 155 + 41 + 10 + 16) \\ &= 250 - 247 = 3\text{ps} \end{aligned}$

| T <sub>d1</sub>         | 0.185 | T <sub>d2</sub>         | 0.155 |

|-------------------------|-------|-------------------------|-------|

| Clk->Q <sub>FF1</sub>   | 0.023 | Setup <sub>FF1</sub>    | 0.038 |

| Clk->Q <sub>FF2</sub>   | 0.025 | Setup <sub>FF2</sub>    | 0.037 |

| Clk->Q <sub>FF3</sub>   | 0.024 | Setup <sub>FF3</sub>    | 0.041 |

| MaxSkew <sub>Ck1-</sub> | 0.015 | MaxSkew <sub>Ck2-</sub> | 0.010 |

| Ck2                     |       | Ck3                     |       |

| Tcycle                  | 0.250 | Jitter                  | 0.016 |

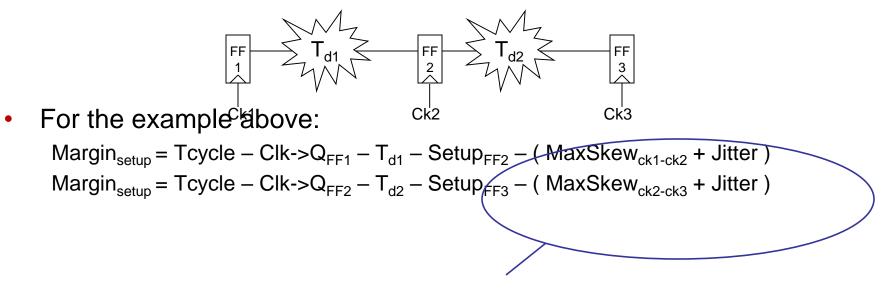

#### How Skew Fits in the Hold Margin Calculation

- Without Skew

- Margin<sub>hold</sub> = Valid<sub>abs</sub> Required<sub>abs</sub>

- With Skew

- Margin<sub>hold</sub> = Valid<sub>abs</sub> Required<sub>abs</sub> MinSkew

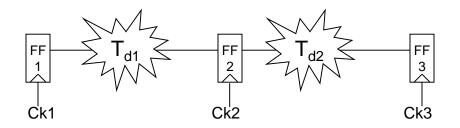

• For the example above:  $C^{k2}$ Margin<sub>hold</sub> = Clk->Q<sub>FF1</sub> + T<sub>d1</sub> - Hold<sub>FF2</sub> - MinSkew<sub>ck1-ck2</sub> Margin<sub>hold</sub> = Clk->Q<sub>FF2</sub> + T<sub>d2</sub> - Hold<sub>FF3</sub> - MinSkew<sub>ck2-ck3</sub>

## Hold Margin Examples

$\begin{aligned} \text{Margin}_{\text{hold FF1->FF2}} &= \text{Clk->Q}_{???} + \text{T}_{d??} - \text{Hold}_{???} - \text{MinSkew}_{???} \\ &= 18 + 55 - 25 - 45 \\ &= 3 \end{aligned}$

$\begin{aligned} \text{Margin}_{\text{hold FF2->FF3}} &= \text{Clk->Q}_{???} + \text{T}_{d??} - \text{Hold}_{???} - \text{MinSkew}_{???} \\ &= 20 + 40 - 28 - 40 \\ &= -8 \end{aligned}$

| T <sub>d1</sub>            | 0.055 | T <sub>d2</sub>     | 0.040         |

|----------------------------|-------|---------------------|---------------|

| Clk->Q <sub>FF1</sub>      | 0.018 | Hold <sub>FF1</sub> | 0.026         |

| Clk->Q <sub>FF2</sub>      | 0.020 | Hold <sub>FF2</sub> | 0.025         |

| Clk->Q <sub>FF3</sub>      | 0.022 | Hold <sub>FF3</sub> | 0.028         |

| MinSkew <sub>Ck1-Ck2</sub> | 0.045 | MinSkew             | Ck2-Ck3 0.040 |

## **Clock Uncertainty Key Notes**

- Always assume worst case skew

- Launching clocks are slow in setup analysis, capturing clocks are fast

- Launching clocks are fast in hold analysis, capturing clocks are slow

- Skew can be minimized by the designer, jitter cannot

- Since skew is related to local clock variation, you can control this by keeping the POD as close as possible

- Jitter is mainly caused by the PLL & the global grid, you can't impact this as a fub designer

- Max skew and Min skew are different

- Min skew is bigger because it must encompass more of the natural variation because a hold failure is fatal

- Max skew is smaller because a setup failure only impacts binsplit

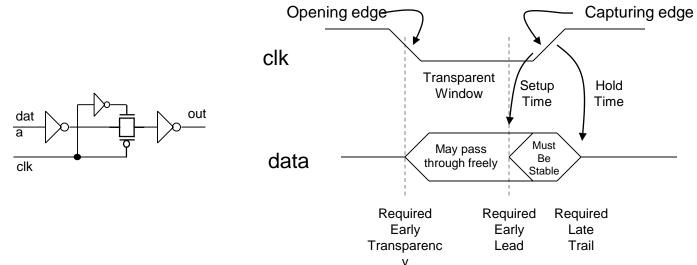

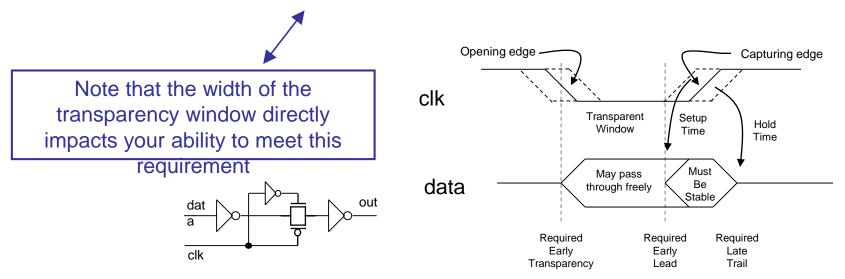

#### What is a Transparency Window?

- Transparency Window

- The time when a data input flows unblocked through a sequential

Inputs may switch anytime in this window, so long as they are valid before the capturing edge of the clock, and remain valid until the hold time (+ skew)

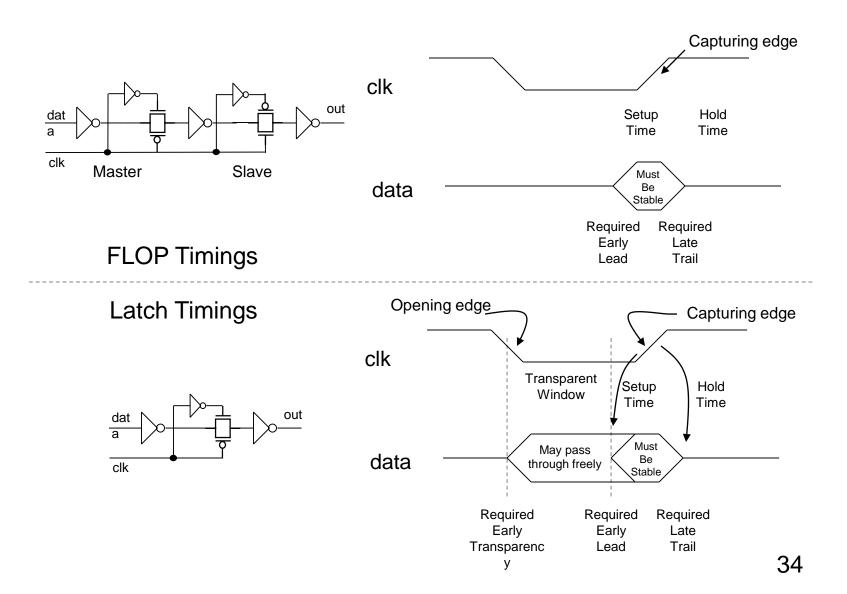

#### Flop vs. Latch Timing Requirements

# A Real World Example of **Transparency** Level sensitive latches allow transparency

- - When the latch opens, data may arrive and pass freely from input to output *without waiting for clock*

- Data only needs to be stable when the latch • closes

- Think of a latch like a street light and a flop light a stop sign. Catch the green and it's a free ride

## Why Transparency Helps

- Transparency reduces the impact of clock uncertainty

- If the opening clock edge is early, the valid time at the output of the latch for a transparent path is *unchanged*

- If the opening clock edge is late, but not as late as the transparent data, the valid time at the output is unchanged

- As long as the data is switching somewhere in the middle of the transparency window, the clock has *no* impact on the timing through this latch

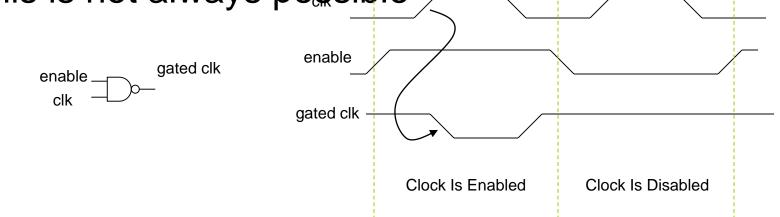

## What Are Gated Clocks?

- When a data signal is used to enable/disable a clock, we call the resulting clock a gated clock

- In general we prefer that the resulting clock timing is dependent only upon the driving clock, not the data

- This is not always possible

## Fullchip Timing Concepts

- Sea of BVRs

- Fullchip RC-Extract

- .rcdly

- Timing Window Propagation

## Sea of BVRs

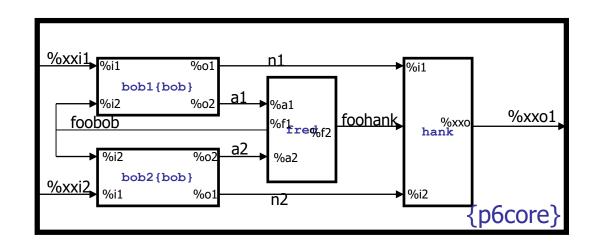

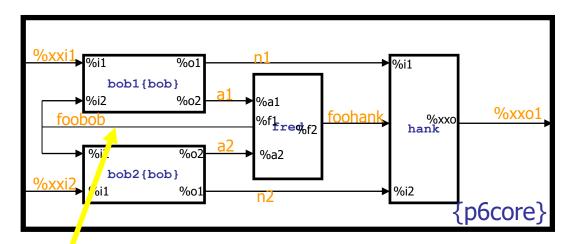

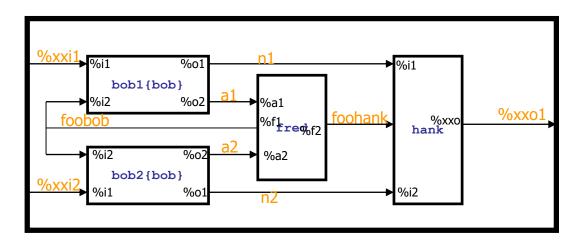

- The block, p6core, contains 4 instances of 3 BVRs (note that BVR "bob" is instantiated twice).

- Note that the node names do not necessarily agree with the pins the nodes connect to.

- Timing/Electrical information for p6core (3 pins) will be coming from p6core.evr.

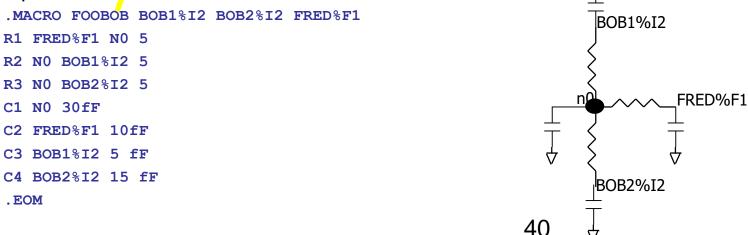

#### Fullchip RC Extract

The nodes in p6 core have RCDLY and need to be timed, but before we can do that we need to extract the Rs and Cs. This occurs during the FC RCEXT. One output format for FC RCEXT is a NTCL file:

#### **RCDLY** generation

- Now that we have the parasitic extraction, we need to compute the delay between the BVRs.

- The specifics on how to generate the RCDLY file will not be discussed here, but here's what a .rcdly file looks like:

- # drivingpin receivingpin MaxRCDlyUp MaxRCDlyDn MinRCDlyUp MinRCDlyDn MaxRcvrSlopeUp MaxRcvrSlopeDn MinRcvrSlopeUp MinRcvrSlopeDn

FRED%F1BOB1%I20.1000.1000.0800.0800.0500.0500.0400.040FRED%F1BOB1%I20.1200.1200.0850.0850.0600.0600.0450.045BOB1%O2FRED%A10.0300.0320.0220.0230.0400.0430.0370.039

SRAM PROJECT: https://www.youtube.com/watch?v=68Dn1x6cZ4g https://www.youtube.com/watch?v=SHJPFNI5Mzo https://www.youtube.com/watch?v=KrqyvpU9Cu0

#### Multiplier -A Comparative Study On Low Power Multiplier Using Microwind Tool

- https://www.youtube.com/watch?v=4-I\_PGPog9o

- <u>https://www.youtube.com/watch?v=MCFG7XD16Ek</u>

- <u>http://www.ijsret.org/pdf/EATHD-15026.pdf</u>

- https://www.youtube.com/watch?v=rqwkrUcNyH4

- <u>https://www.youtube.com/watch?v=4-I\_PGPog9o</u>

- https://www.youtube.com/watch?v=WxSR2Yhnqk4&t=30s

- https://www.acsu.buffalo.edu/~phaniram/bootstrap-prestructure22\_files/images/paper\_1.pdf